ПРИНЦИПИАЛЬНАЯ СХЕМА ПВК

Плата управления УФРК

Плата управления (ПУ) обеспечивает управление режимами запроса, местное включение режимов запроса и световую индикацию режимов запроса. Принципиальная схема платы ПУ приведена в альбоме схем. На плате ПУ установлены элементы управления режимами работы УФРК (тумблеры В1…В6) и элементы световой индикации режимов запроса (VD1...VD4). При местном управлении режимы запроса включаются тумблерами В1, В3, В5 и В6, при этом тумблер В2 должен быть в положении "Местн". При дистанционном управлении УФРК тумблер В2 должен быть установлен в положение "Дист". В качестве элементов индикации используются светодиоды типа 3Л102Б.

Плата счетчика УФРК

Принципиальная схема платы счетчика (ПС) приведена в альбоме схем. Плата ПС содержит в своем составе счетчик интервалов времени, генератор тактовых импульсов, пусковое устройство, делитель частоты и дешифратор импульсов τ1775. Одиннадцатиразрядный счетчик интервалов времени выполнен на триггерах У9…У19 с развязывающими вентилями У1-1, У1-2,…, У6-1, У6-2 на выходах каждого разряда счетчика.

Тактовые импульсы на счетчик поступают с кварцованного генератора, работающего на частоте 15 МГц и выполненного на элементах У27-1, У27-2, У27-3. Предварительное деление частоты генератора на 15 осуществляется делителем частоты, собранным на элементах У29–У33. Схема счетчика параллельного действия с последовательным переносом позволяет снимать двоичные коды со всех разрядов одновременно, без задержки. Цикличность работы счетчика определяется импульсами запуска τ0 и τ1775, которые устанавливают старт-стропный RS-триггер (пусковое устройство), выполненный на элементах У28 (У28-1…У28-4), в единичное и нулевое состояние соответственно. Импульс 1775 формируется дешифратором на элементах У7-1, У6-3, У6-4, У8, У7-2, У20 (У20-1,У20-2).

В плате ПС использованы ИС 130 и 133 серий: 130ЛА3, 130ТВ1, 133ЛА1-133ЛА4, 133ЛА6, 133ТВ1.

Плата дешифраторов импульсов УФРК

Принципиальная схема платы ПДИ приведена в альбоме схем. Плата ПДИ предназначена для формирования импульсов с требуемой временной расстановкой относительно импульса τ0.

Формирование импульсов осуществляется по схеме двухступенчатого дешифратора: для τ5 – элементы У4, У5-1, У3-3; У3-4, У5-2; для 9 – У6, У7-1, У8-1, У8-2, У7-2; для 14 – У9, У10-1; У8-3, У8-4, У10-2; для 28 – У11, У12-1, У13-1, У13-2, У12-2; для 33 – У14, У15-1, У13-3, У13-4; У15-2; для 1755 – У16, У17-1, У18-1, У18-2, У17-2; для 23 – У19, У20-1, У21-1, У-21-2, У22-1. Линия задержки Л31 импульсов τ23 – и элементы У21-3, У21-4, У20-2 обеспечивают дополнительную задержку импульсов τ23 на 0,4 мкс.

Длительность сформированных импульсов определяется длительностью импульса, снимаемого с выходов младшего разряда, и равна 1 мкс. В плате ПДИ использованы ИС 133 серий: 133ЛА1-133ЛА3, 133ЛА8.

Плата формирования кодов УФРК

Принципиальная схема платы ПФК приведена в альбоме схем. Плата ПФК предназначена для формирования кодов запроса и сигналов включения световой индикации режимов запроса.

Рассмотрим работу платы ПФК на примере формирования кода и соответствующего ему сигнала световой индикации. Код формируется из импульсов τ14 и τ23,4, стробируемых сигналом "Имп N". Импульсы τ14 и τ23,4 поступают на вход элемента У2-1, а с него на вход схемы совпадения У2-2, на второй вход которой поступает сигнал "Имп N" с длительностью, равной рабочему стробу. С выхода элемента У2-2 импульсы через элементы У5-1 поступают на вход выходного усилителя У11. В качестве выходного усилителя для согласования выходных сигналов с нагрузкой (кабель с волновым сопротивлением 75 Ом) применен магистральный усилитель, выполненный на ИС 109ЛИ1.

Импульсы τ14 и τ23,4 поступают также на элементы У1-1 и У1-2 соответственно. Импульсом с выхода элемента У1-3, который формируется при совпадении на входе импульса τ14 и первого импульса кода №, поступающего с элемента У5-2, устанавливает в единичное состояние триггер на элементах У4-2, У4-3. В исходное состояние этот триггер возвращается импульсом с выхода элемента У4-1, который формируется при совпадении на входе импульса τ23,4 и второго импульса кода N. Из импульса триггера схема на элементах У4-4, У8-1 формирует сигнал, который через инвертор У8-2, схему совпадения У6-1 (на второй вход которой поступает сигнал разрешения "Имп N"), инвертор У6-2 устанавливает триггер У15-2 в единичное состояние. С прямого выхода триггера У15-2 положительный потенциал поступает на элемент индикации У16-2, в выходную цепь которого через резистор R6 включен светодиод VД1, установленный в плате управления.

В нулевое состояние триггер У15-2 устанавливается импульсом, формируемым генератором на элементах У9-1, У9-2, У9-3, У9-4 и схемой формирования короткого импульса на элементах У10-1, У10-2. На выход сигнал индикации также поступает с инверсного выхода триггера У15-2 через инвертор У14-4 и выходной усилитель У20.

Аналогичным образом работает плата ПФК при формировании кодов запроса в режимах "Н", "V", "К".

В плате ПФК использованы ИС 109 и 133 серий: 109ЛИ1, 133ЛП1, 133ЛА3, 133 ЛА4, 133ЛА7, 133ТМ2.

Плата дешифратора режимов УФРК

В состав платы дешифратора режимов (ПДР) входит пусковое устройство, генератор опроса, распределитель тактов, дешифратор режимов, а также формирователь рабочего строба. Плата ПДР дешифрирует режимы запроса и формирует импульсы включения кодов запроса "N", "Н", "V", "К".

Принципиальная схема платы ПДР приведена в альбоме схем. Импульс τ1775 устанавливает R-S-триггер с инверсными входами, выполненный на элементах У1-2, У1-3 в единичное состояние. Уровень логической единицы с выхода У1-2 разрешает работу генератора опроса, выполненного по схеме мультивибратора на элементах У4-1, У4-2, У4-3, У4-4. Мультивибратор работает в режиме самовозбуждения с частотой повторения, равной 166 кГц. Импульсы мультивибратора поступают на формирователь на элементах У3-1, У3-2, который формирует по их срезу сигналы, поступающие через инвертор У3-3 на счетные входы кольцевого сдвигающего регистра, используемого в качестве распределителя тактов. Распределитель тактов выполнен на R-S-D-триггерах У6, У8 и элементах У11-1, У10-4, выполняющих роль цепи обратной связи. R-S-D-триггер имеет информационный вход D, динамический вход С и несинхронные S и R входы. Если на вход D поступает сигнал логической единицы, то после прихода на вход С очередного импульса генератора опроса, триггер устанавливается в единичное состояние. Если из R-S-D-триггеров составить замкнутую цепь, в которой выход каждого из них соединен с входом D последующего, а все входы С подключены к общей шине, то каждый раз с приходом очередного импульса генератора опроса, информация, хранящаяся в предыдущем триггере, будет переходить в следующий. Дойдя до конца регистра, логическая единица возвращается на вход D первого триггера и счет повторяется.

Импульс установки регистра в исходное состояние формируется схемой на элементах У5-1, У5-2, У5-3 и подается на R-входы триггеров У6-2, У8-1, У8-2 через элементы У5-4, У3-4, а на S-вход триггера У6-1 через схему равнозначности, выполненную на элементах У9-1, У9-2, У9-3, У9-4 и У10-1. Схема подавления ложного состояния 1111 выполнена на элементах У11-1, У10-4, а для подавления ложного состояния – 0000 используются элементы У10-2, У10-3, У12, У13-1, У13-2, У13-3. Если все триггеры находятся в запрещенном состоянии, то схема на элементе У7 с поступлением на плату ПДР импульса запуска τ0 формирует сигнал, который через элементы У5-4, У3-4 переводит распределитель тактов в исходное состояние 1000.

Такты опроса "N", "Н", "V", "К" поступают на коммутаторы: на элементы У14, У16-1 поступает такт "N", на элементы У19, У16-2 – такт "Н", на элемент У21 – такт "V", на элемент У22 – такт "К". На остальные входы коммутаторов поступают сигналы управления режимами запроса с платы ПУ при местном управлении и извне – при дистанционном управлении. Если обнаружено соответствие заданного режима запроса, то соответствующий ему формирователь на элементах У23-3, У23-4 или У24-3, У24-4 или У25-3, У25-4 или У26-3, У26-4 из уровней логических единиц, поступающих с инверторов У17-3, У20-3, У17-4, У20-4, формирует импульс совпадающий по времени с фронтом перепада уровня логической единицы. Через схемы У27-1, У1-1 этот импульс устанавливает пусковое устройство (R-S- триггер на элементах У1-2, У1-3) в нулевое состояние, тем самым с генератора опроса снимается потенциал, разрешающий его работу. Далее распределитель тактов не переключается и остается в состоянии такта опроса, соответствующего выявленному режиму запроса. Уровень логической единицы, снимаемый с одного из инверторов У17-3, У20-3, У17-4, У20-4, в соответствии с выбранным тактом опроса, стробируется по длительности рабочим стробом. Формирование рабочего строба осуществляется триггером, выполненным на элементах У2-2, У2-3, У2-4. Стробирование осуществляется схемами совпадения У23-1, У24-1, У25-1, У26-1, с выхода которых сигналы через инверторы У23-2, У24-2, У25-2, У26-2 выдаются в виде импульсных сигналов режимов N, H, V, K на выход платы. Триггер рабочего строба устанавливается в единичное состояние импульсом запуска о и возвращается в исходное состояние импульсом τ33.

В плате использованы ИС 133-й серии: 133ЛА1…133ЛА4, 133ЛР1, 133ЛР4, 133ТМ2.

Стабилизатор напряжения УФРК

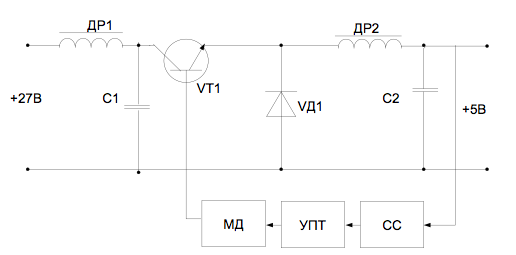

Для питания УФРК стабилизированным постоянным напряжением +5 В используется стабилизатор СН-616. Первичное напряжение +27 В на стабилизатор поступает с выпрямителя ПВ-13. Функциональная схема стабилизатора напряжения СН-616 приведена на рисунке 3.13.

В состав функциональной схемы входят предварительный фильтр Др1, С1, регулирующий элемент VТ1, входной фильтр Др2, С2, схема сравнения (СС), усилитель постоянного тока (УПТ) и модулятор длительности (МД. Стабилизатор представляет собой систему автоматического регулирования с регулирующим элементом, работающим в ключевом режиме.

Стабилизация выходного напряжения при изменении напряжения +27 В осуществляется за счет изменения длительности открытого и закрытого состояния регулирующего элемента VТ1.

Длительность пребывания VТ1 во включенном состоянии может регулироваться. Обозначим время пребывания транзистора VТ1 во включенном состоянии через t1, а в выключенном состоянии – через t2. Тогда среднее значение выходного постоянного напряжения Uср определяется соотношением

где Uвх – входное напряжение. Для удобства дальнейших рассуждений выражение (3.1) преобразуем к виду

Из выражения (3.2) видно, что изменением времени t1 можно компенсировать изменение входного напряжения Uвх. таким образом, чтобы среднее значение выходного напряжения оставалось бы постоянным. Для стабилизации выходного напряжения необходима автоматическая регулировка длительности времени t1 в зависимости от изменения входного напряжения +27 В.

Управление транзистором VT1 осуществляется с помощью модулятора длительности, преобразующего сигналы, поступающие с выхода УПТ в последовательность импульсов тока переменной скважности. УПТ производит усиление сигнала рассогласования, вырабатываемого путем сравнения выходного напряжения с опорным, сформированным в схеме сравнения. Предварительный фильтр Др1, С1 сглаживает пульсации входного напряжения, поступающего на выход через VT1. Диод VD1 предназначен для разряда реактивной энергии дросселя Др2 через сопротивление нагрузки во время закрытого состояния VT1.

Плата формирователя импульсов ПВК

Плата ФИ предназначена для формирования поступающих с УФРК импульсов по амплитуде. Принципиальная электрическая схема платы приведена в альбоме схем.

На вход платы ФИ поступают с УФРК видеоимпульсы установленного кода с амплитудой не менее 2,4 В и длительностью 1,0 мкс. Пройдя через эмиттерный повторитель на транзисторе VT9, видеоимпульсы с его нагрузки R18 подаются далее на предварительный импульсный резистивный усилитель на транзисторе VT7. Этот усилитель охвачен глубокой отрицательной обратной связью по переменной составляющей тока эмиттера, что позволяет устранить искажения вершины импульса. С3 – ускоряющий конденсатор, который уменьшает длительность фронта импульсов на выходе усилителя. Диод VD3 обеспечивает восстановление постоянной составляющей усиливаемых импульсов на выходе усилителя, то есть каждый выходной импульс начинается с нулевого уровня напряжения. Резистор R14 является нагрузкой усилителя. Дальнейшее прохождение усиленных видеоимпульсов разделяется на два канала: прямой и задержанный. Каждый из каналов собран по идентичной схеме, в состав которой входят входной эмиттерный повторитель, резисторный усилитель и выходной эмиттерный повторитель. В задержанном канале имеется также линия задержки ЛЗ1 на 0,5 мкс. С выходов платы ФИ задержанные импульсы с амплитудой 20 В поступают на "Выход 1 мкс", а не задержанные импульсы с той же самой амплитудой – на "Выход 2 мкс".

Возбудитель ПВК

Возбудитель предназначен для генерирования СВЧ колебаний стабильной частоты. Основные технические параметры возбудителя:

- несущая частота 837,5 МГц;

- нестабильность несущей частоты ±0,01%;

- ыходная импульсная мощность не менее 1,3 Вт.

Принципиальная схема возбудителя представлена в альбоме схем. В состав схемы возбудителя входят:

- задающий кварцевый генератор на транзисторе VT1;

- двухкаскадный усилитель мощности на транзисторах VT3, VT5;

- удвоитель частоты на транзисторах VT6, VT7;

- трехкаскадный усилитель мощности на транзисторах VT9, VT2, VT4;

- варакторный утроитель частоты на диодах VD1 и VD2;

- стабилизатор напряжения + 12,6 В на транзисторе VT8.

Кварцевый автогенератор собран на транзисторе VT1 по емкостной трехточечной схеме с кварцевым резонатором в цепи положительной обратной связи. Транзистор VT1 включен по схеме с общей базой, конденсатор С1, замыкает базу VT1 на корпус по высокой частоте. Нагрузкой автогенератора является резонансный контур L1, С3, С4, включенный в цепь коллектора VT1. С помощью емкостного делителя С3, С4 подбирается требуемый коэффициент обратной связи. Режим транзистора VT1 по постоянному току задается с помощью резисторов R1, R2, R4, R5. Цепочка R4, С6, С7, С11 служит для развязки автогенератора по цепи питания. Индуктивность L2 компенсирует статическую емкость кварцевого резонатора ПЭ1 и позволяет произвести начальную установку частоты автогенератора при настройке. Сигнал с выхода автогенератора снимается с коллектора транзистора VT1 через емкость С10 и усиливается двухкаскадным усилителем мощности на VT3 и VT4. Первый усилитель мощности на транзисторе VT3 собран по схеме с общим эмиттером. Коллекторной нагрузкой усилителя является одиночный колебательный контур L5, C15, C16, зашунтированный резистором R28 с целью расширения полосы пропускания. Режим работы каскада по постоянному току обеспечивает замыкание эмиттера VT3 на корпус по высокой частоте. конденсатор С17-фильтр по цепи питания. С емкостного делителя С15, С16 сигнал с выхода первого усилителя поступает на вход второго усилителя. Второй усилитель мощности на VТ5 собран по схеме с общим эмиттером на транзисторе типа 2Т606 с нагрузкой в виде двухконтурного полосового фильтра на элементах L8, L9, C25, C28, C29, C30, C31. Частичное включение контуров полосового фильтра через емкостные делители С25, С28, С30, С31 позволяет согласовать выходное сопротивление усилителя с входным сопротивлением удвоителя частоты. Режим усилителя по постоянному току задается резисторами R11, R12, R13, R14. Цепочка R13, С21, Др3 используется для развязки каскада по цепи питания.

Каскад на транзисторе VT6 работает в режиме удвоителя частоты, собран по схеме с общим эмиттером. полосовой фильтр на элементах L10, L11, C33, C34, C36 настроен на вторую гармонику входного сигнала. Смещение рабочей точки достигается за счет падения напряжения на параллельно включенных резисторах R16, R17 в эмиттерной цепи транзистора. Емкость С35 применена для развязки удвоителя по цепи питания.

Каскад на транзисторе VT7 работает в режиме удвоения частоты входного сигнала. Выходной полосовой фильтр построен на элементах L12, L13, С48, С49, С50. Смещение рабочей точки транзистора осуществляется за счет падения напряжения на резисторе R18 в эмиттерной цепи. Через цепочку Др6, С38 на коллектор транзистора подаются прямоугольные импульсы амплитудой 24 В положительной полярности с длительностью =2 мкс. С выхода удвоителя ВЧ сигнал поступает на трехкаскадный усилитель мощности на транзисторах VT9, VT2, VT4. Все каскады усилителя мощности собраны на схеме с общим эмиттером и коллекторными нагрузками в виде последовательного колебательного контура. Транзисторы VT2 и VT9 типа 2Т904А, транзистор VT4 – типа 2Т907А. Режим работы транзисторов VT2, VT9 задается резисторами R3, R26, R27, R29, R23, R30. Смещение рабочей точки транзистора Т4 обеспечивается за счет падения напряжения на резисторе R10. С выхода усилителя мощности на транзисторе VT4 ВЧ сигналы с мощностью Р=5…6 Вт подаются на варакторный утроитель частоты, который собран по последовательной схеме на диодах VD1 и VD2. Нагрузкой утроителя является трехзвенный фильтр Э1, Э2, Э3. Шунтирование высших гармоник сигнала на входе умножителя осуществляется емкостью С27. Смещение рабочей точки диодов автоматическое, за счет падения напряжения на резисторе R15. С выхода умножителя сигнал подается на разъем Ш2 и далее на циркулятор Ц1, обеспечивающий развязку высокочастотных цепей и направленную передачу ВЧ мощности. Для питания каскадов на транзисторах VT1 и VT3 в возбудителе используется собственный стабилизатор напряжения +12,6 В, собранный на стабилитронах VD3, VD4 и транзисторе VT8.

Высокочастотные контуры каскадов усиления по мощности ПВК

Принципиальные схемы ВЧ контуров I и II каскадов усиления, а также каскада усиления III, представлены в альбоме схем. Контур ТЖ2.062.061 предназначен для работы в первых двух каскадах усилителей ПВК.

Основные технические данные I и II каскадов усиления:

- коэффициент усиления по мощности – 20…40;

- коэффициент стоящей волны входа – 3;

- средняя подводимая мощность – 25 Вт.

Входной контур выполнен в виде полосового фильтра, его возбуждение осуществляется комбинированным индуктивно-емкостным зондом. В анодном резонаторе коаксиального типа размещен цилиндрический конденсатор переменной емкости для настройки контура. Отбор мощности из анодного резонатора осуществляется с помощью петли связи. Регулировка связи производится путем изменения погружения петли в резонатор. Контур ТЖ2.062.066 предназначен для работы в третьем каскаде усиления ПВК.

Основные технические данные:

- коэффициент усиления по мощности – 10…12;

- коэффициент стоячей волны входа – 3;

- выходная мощность – 3…5 кВт;

- допустимое постоянное анодное напряжение – 4,2 кВ.

Входной контур выполнен в виде полосового фильтра. Возбуждение входного контура осуществляется комбинированным индуктивно-емкостным зондом. В анодно-сеточном резонаторе размещен цилиндрический конденсатор переменной емкости для оперативной настройки контура. Отбор мощности из анодно-сеточного резонатора осуществляется с помощью емкости связи. Регулировка связи производится при настройке по максимуму выходной мощности.